INTERNATIONAL JOURNAL OF RESEARCHES IN BIOSCIENCES, AGRICULTURE AND TECHNOLOGY

© VMS RESEARCH FOUNDATION www.ijrbat.in

# EFFECTIVE REGULATION OF VOLTAGE AND REACTIVE POWER COMPENSATION USING 12 PULSE STATIC SYNCHRONOUS COMPENSATOR (STATCOM)

Nimbalkar Priti. N. and Prashant Thakre

Department of Electrical Engineering, Abha Gaikwad Patil College of Engineering, Nagpur , India Department of Electrical Engineering, Abha Gaikwad Patil College of Engineering, Nagpur , India pritinimbalkar077@gmail.com, pvthakre2011@gmail.com

## **ABSTRACT:**

12 pulse gate turn-off controller-themed technology along voltage source converter unit integrated with 6 pulse VSC as a preliminary model of GTO firing unit has made Static Synchronous Compensator (STATCOM), a FACTS controller as a better option for voltage regulation and reactive power improvement at the point of common coupling of the transmission line using the shunt compensation technique. A complete model simulated in a MATLAB environment is included in this paper.

Key words: - VSC , GTO, STATCOM , MATLAB

# I. INTRODUCTION:

The advancement of integrated power electronics devices made a great significant contribution to the performance of overall improved power system quality and reliability into value-based transmission and generation planning scenarios.[1,2].

Several power electronics control-based techniques have been implemented to ride over the poor voltage control methodology of handdriven control techniques which suffer from a delay in switching capabilities with greater switching losses and lowering power factor of the overall system. Gate turn-off Thyristor STATCOM controller (GTO ) has made a proven advantage in the field of FACTS controller for quick response time, better performance for higher regulated power flow.

Modified GTO-based STATCOM utilizes a multipulse converter technique by adding several converter units switched with fundamental frequencies [3,4].

The STATCOM with voltage source converter (VSC) with the implementation of Gate Turn Off device (GTO) has made easy control over the harmonic reduction and voltage stability in transmission and distribution system network [5]-[11].

STATCOM with VSC GTO gives a better contribution for various critical system conditions such as power instability, unregulated power due to overloading or underloading conditions. , transients due to uneven system loading parameters through a better approach of control by phase angle control and limiting the amplitude of voltages at the system.[12]-[14]

#### **II. OPERATING PRINCIPLE OF STATCOM**

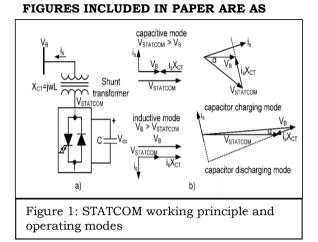

Fig. 1 (a) shows the STATCOM single 1 line diagram showing a Gate turn Off thyristor assembly with an antiparallel diode [15]. Shunted with a transmission line by a shunt transformer or coupling transformer having a leakage reactance  $X_{CT}$ . On the DC side, a capacitor C, providing a stiff dc voltage  $V_{dc}$ , is capable to sustain the charge and discharge current which is, in turn, useful for switching gate sequence stages of converter valves useful in reactive power compensation by different modes of operations by injecting and absorbing the required power via capacitive and inductive mode as shown in fig. The PWM and frequency control techniques are used for distortion fewer harmonics at the PCC can be found using multilevel and multi-pulse technique. [16]-[19].

Figure 1.(b)  $V_B$  denotes the system voltage of AC system where  $V_{STATCOM}$  denotes the STATCOM output voltage. Three modes are seen to be implemented for power and voltage regulation at the point of interfacing, When  $V_B > V_{STATCOM}$ , The STATCOM operated in Inductive mode , hence reactive current move from system to STATCOM to AC system, reversal of current will be done when  $V_{STATCOM} > V_B$  hence STATCOM provides reactive power to system and acts in capacitive mode . when  $V_{STATCOM} = V_B$  means both are having equal magnitude the system is said to be in stable state or in steady state.

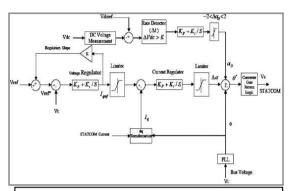

From the fig.2 initially, a voltage measurement is done by a voltage measurement unit which measure's AC system voltage  $V_M$  which is compared with some set reference value of voltage as given in fig as  $V_{ref}$ . Similarly, measurement of AC current is also done. Initially, the values are in the form of instantaneous abc which are then turned into d-q form. Basically line voltage passing through, positive sequence fundamental line voltage calculator block gives AC voltage ( $V_M$ ) is given as,

$$V_M.=\sqrt{(V_{md})^2+(V_{mq})^2}$$

.....(05)

The two proportional and integral Controllers are being introduced in the converter circuit as AC voltage regulator circuit and current regulator circuit.

The main voltage and reference voltage are promoted to AC voltage regulating circuit of PI controller which is nothing but an outer control loop. After comparing both the values of voltages, a reference reactive current is  $I_{qref}$  is then forward to the internal current control regulatory loop is given as ,

$$I_{shq}(k) = I_{shq}(k-1) + K_p[V_{Mer}(k) - V_{Mer}(k-1)] + K_I V_{Mer}(k) \qquad (01)$$

$V_{Mer}(k) = V_{M*}(k) - V_M(k)$  .....(02)

Current regulatory loop tallies the reference reactive current  $I_{qref}$  with the reactive component of measured current from AC system  $I_q$ .

DC link potential controller after comparing the error signal following equation are find out

| $I_{shd}(k) = I_{shd}(k-1) + K_p[V_{dcer}(k) - V_{dcer}(k-1)]$ |

|----------------------------------------------------------------|

| $1)] + K_{I}V_{dcer}(k) \dots (03)$                            |

| $V_{dcer}(k) = V_{*dc}(k) - V_{dc}(k)$ (04)                    |

Where  $K_p$  and  $K_l$  are gains of Proportion and integral Controller units.

Fig.2 Block diagram (b) Controller with d-q current coupled with converter gate pattern logic methodology.

Both AC voltage regulator & DC regulator are important for balancing the point of common coupling voltage of AC system.  $I_{shd}$  and  $I_{shq}$  of STATCOM hence plays major role for maintaining requisite reactive power to system, and

calculating the values of hence we get the output voltage of converter . Simulation results are shown in fig 6.

Hence, we can get the Modulation index (M) from above equations,

And the Phase angle  $\propto$  is given by

Hence with varied loading conditions the optimized output of desired reactive current can be find out.

The compared values of reactive reference current and quadrature current from AC system give rise to a phase angle,  $\alpha$ , which is finally approaches to a pulse generator.

DC regulator is responsible for controlling the real power which is often utilized to compensate the internal losses.

The objective of adapting the d-q current control strategy of this control scheme is to initiate synchronous output voltage waveform and to maintain VSC output voltage[20], in such a way as to carry reactive as well as active power flow to keep the DC link voltage at a constant value[21-22].

PWM technique for active and reactive power control is well illustrated in . An inevitable delay is persisted in feedback of voltage regulating loop, shows one cycle of the line voltage in its response time than reactive current controller[23-24].

## III: PHASE LOCK LOOP [PLL] IMPLEMENTATION TECHNIQUE

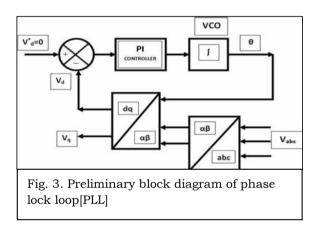

Fig 3 shows preliminary block diagram of phase lock loop, initiating from voltage-controlled oscillator (VCO) actuating with free running frequency is in resonance with the nominal frequency of the input reference voltage.

For any particular instant to send active current to the transmission line, system voltage and active current should be in phase with each other, requires to create a signal in reference. which will adjust to set itself in phase with actual voltage. After getting the knowledge of angle information we can produce the current reference for active and reactive power problem.

Open loop control method is not suitable during critical operating System conditions like surges and spikes, and distortional waveforms occurs at the PCC results in incorrect angle computation is done at the output of PLL. Hence closed loop PLL system is utilized for this controller regulatory system.

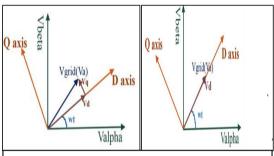

From fig 4. it is clear during alpha beta to d-q transformation system voltage non coincide along direct axis, This voltage is make aligned with direct axis to get non zero quantity of direct and quadrature axis voltage by adapting PI control technique to get  $V_q = 0$ , along with that  $\omega$ t with respect to  $V_{alpha}$  in turn change its position and get a contemporary value along d axis is utilized to promote Sin and Cosine functions to foster active and reactive components.

# IV: 12 PULSE SIMULATION TEST MODEL CONFIGURATION AND WORKING TRAITS

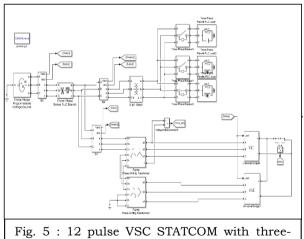

Fig 5 shows 12 pulse VSC STATCOM, the simulation control employs for a 230kV, (1 p.u.) as a main AC supply system with short circuit

level margin of10000 [MVA], and a varied reference value is kept as 236.9 kV with 1.03 p.u., DC link capacitor reference voltage is kept in per unit capacity(2.4 p.u.) with 552kV. Three Phase LC load is employed at interval of 2 seconds. load 1: with active power = 1p.u. and reactive power = 0.8 p.u.), load2 : with active power of 0.7 p.u. and reactive power = 0.5 p.u.), load 3 : with active power 0.6p.u. and reactive power 0.4 p.u.) the total simulation upto 8 seconds shown for different parameters are shown in fig 6 to fig 10.

## **V: RESULT AND DISCUSSION**

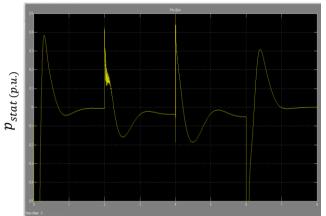

The core objective implementing this simulation technique is to provoke DC link capacitor voltage stagnant while keeping voltage of point of interface (PCC) between the distribution line within bounds.

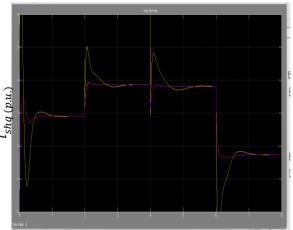

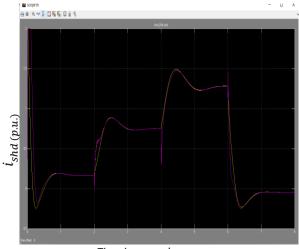

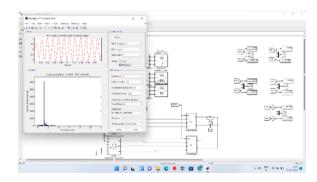

The main voltage of Ac system  $V_M$  and  $V_{dc}$  both are major inputs penetrates at the comparator along with their reference values to get an error in the signals for direct and quadrature shunt currents  $i_{shd}$  and  $i_{shq}$  shown in figure7. After simulation the gain values of reference current can be tracked. Total Harmonics distortions values are found less than 6 pulse VSC STATCOM MODEL shown in fig.11 & fig12.

Figure. 5 shows ,For receiving less distortion and the better voltage sinusoidal output, coupling transformer with multipulse method is being utilized in 12 pulse firing technique of this GTO VSC converter for STATCOM. Duel unit of zig-zag phase-shifting transformer is connected in series to get a versatile converter, one transformer with primary as star -star and other with a star with a delta winding along secondary side. Each 6 pulse VSC converter creates duel voltages which are 30 deg. Apart in phase with each other. Overall six phase legs are amended on the only DC line . STATCOM THD occurs for voltages found to be 6.6.-8.8 percent . The Current characteristics show the overall THD 8.69- 12.50 percentage. The values of peak overshoot of final voltage output lays in 0.0045-2.45. settling time variation is from 0.33 to 0.577 seconds. All the values mentioned here are in per unit.

#### **VI.CONCLUSION**:

STATCOM provided better reactive power compensation even at the unbalanced load and try to regulate the PCC bus voltage relative to reactive and active power flow.12 pulse Simulation model regulates power to control more better way than 6 pulse and the combined effect of harmonics are reduced for better level than uncompensated line .Although THD of STATCOM output voltage is required to be reduced up to the IEEE standard hence more pule techniques should be implemented to enhance the better results However the reactive power control at the PCC terminals are find more regulated mode during implementation of both the modes of STATCOM as capacitive and inductive during simulation under MATLAB.

#### **REFERENCES:**

[1] L. Xu and V. G. Agelidis," Flying capacitor multilevel PWM converter based UPFC", IEE hoc.-Elects Power. Appl., Vol. 149, No 4, , pp. 304-310, July 2002.

[2] A. Ajami, M. R. Jannati-Oskuee, A.

Mokhberdoran, and A. Van Den Bossche, "Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches," IET Power Electron., vol. 7, no. 2, pp. 459–466, Feb. 2014

[3] Zhang Z, Kuang J, Wnag X, Ooi BT (1993) Forced commutated HVDC and SVC based on phase -shifted multi -conveter module , IEEE Trans. Power Delievery 8(2): 712-718.

[4] Fujita H, Tominaga S, Akagi H(1996) Analysis and design of a dc voltage -controlled static var compensator using quad-series voltage source invetres . IEEE Trans. Ind. Appl. 32(4):970-978.

[5]N. G. Hingorani, "Power electronics in electric utilities: role of power electronics in future power systems," Proceedings of the IEEE, vol. 76, pp. 481, 1988.

[6] N. G. Hingorani and L. Gyugyi, Understanding FACTS: concepts and technology of flexible AC transmission systems: IEEE Press, 2000.

[7] L. Gyugyi, "Dynamic compensation of AC transmission lines by solid-state synchronous voltage sources," IEEE Transactions on Power Delivery, vol. 9, pp. 904, 1994.

[8] L. Gyugyi, "Reactive Power Generation and Control by Thyristor Circuits," IEEE Trans. Ind. Appl., vol. IA-15, no. 5, pp. 521-532, Sept./Oct., 1979.

[9] "Evaluation of Advanced Static VAR Generators," EPRI Report No. EL3397, May 1984.

[10] C.W. Edwards et al., "Advanced Static Var Generator Employing GTO Thyristors," IEEE, PES Winter Power Meeting, Paper No. 38WM109-1, 1988.

[11] L.Gyugyi et al. "Advanced Static Var Generator Employng GTO Thyristors," IEEE, PES Winter Power Meeting, Paper No.38WM109-1, 1998

[12] N. G. Hingorani and L. Gyugyi, Understanding FACTS, Concepts and Technology of Flexible AC Transmission Systems. Piscataway, NJ: IEEE Press, 2000.

[13] R. Mohan and R. K. Varma, Thyristor-Based FACTS Controllers for Electrical Transmission Systems. Piscataway, NJ: IEEE Press, 2002.

[14] Y. Liang and C. O. Nwankpa, "A new type of STATCOM based on cascading voltage-source inverter with phase-shifted unipolar SPWM," IEEE Trans. Ind. Appl., vol. 35, no. 5, pp. 1118–1123, Sep./Oct. 1999.

[15] D.A.N. Jacobson , R.W. Menzies . " Comparison of thyristor switched capacitor and voltage source GTO invetrter type compensators for single phase feeders ", IEEE transactions on Power Delivery, 1992.

[16] Narain G. Hingorani, Laszlo Gyugyi, "Understanding FACTS", IEEE press 2000. 5Yong Hua Song, Allan T. Johns, "Flexible AC transmission systems FACTS", IEE Power and energy Series 30,1999.

[17] Zhiping Yang, "Integration of battery energy storage with Flexible AC transmission system devices", Ph.D Thesis, University of Missouri-Rolla, 2000.

[18]Amir H. Norouzi, "Flexible AC Transmission Systems: Theory, Control and Simulation of the STATCOM and SSSC", MSc Thesis, University of New Brunswick, March 2003.

[19] Ekanayake, J. B., Jenkins, N., "A three advanced static var compensator", IEEE Trans. on Power Delivery, Vol. 11, no.1, pp.540-545.

[20] Natrajan Prabaharan, Kaliannan Palanisamy," A comprehensive review on reduced switch multilevel inverter topologies , moduction techniques and applications", Renewable ansd sustainable Energy Reviews, 2017.

[21] Yam. C.M. " A SVD based controller UPFC for power flow control ", Eletric Power Systems Research , 2004-06.

[22] B. Singh and V. S. Kadagala, "Simulation of three-level 24-pulse voltage source convertersbased static synchronous compensator for reactive power control," IET Power Electronics, vol.7, no. 5, pp. 1148–1161, 2014.

[23] C. Schauder , M.Gernhardt, E. Stacey ,

T.Lemak, L. Gyugyi, T.W. Cease, A. Edris.

" Operation of ± 100 MVar TVA STATCON", IEEE

Transactions on Power Delievery , 1997.

[24] Garcia P. and Garcia A., 2000, "Control System for a PWM-Based STATCOM", IEEE Trans. on Power Delivery, g, 1252-1257.

phase loads System.

Fig.2 Block diagram (b) Controller with dq current coupled with converter gate pattern logic methodology

Fig.4 vector diagram for d-q voltages from alpha to beta voltages

Time in seconds Fig 6:  $(i *_{shq} and I_{shq})$  Output at equal time interval of 2 seconds

Page 61

Time in seconds Fig 7:  $(i *_{shd} and I_{shd})$  Output at equal time interval of 2 seconds

Time in seconds Fig.8: Active power  $(P_{stat})$  output of STACOM Converter at varied load with respect to time

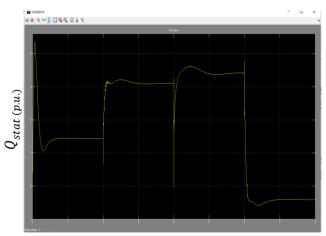

Time in seconds Fig9: Simulation output of Reactive power  $(Q_{stat})$  output of STACOM converter at varied load

© 🛈 🛇

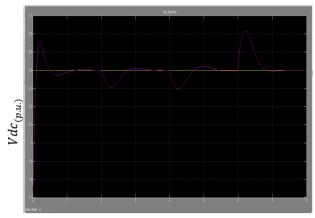

Time in seconds Fig 10. Simulation output for DC link voltage (Vdc)

Time in seconds

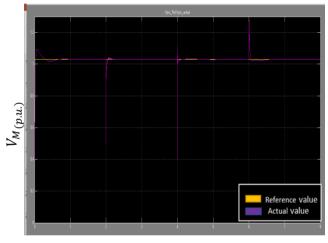

Fig 11. Simulation output for PCC voltage AC System ( $V_M$ ) actual voltage & ( $V_M$ \*) reference voltage

Fig:11 Fast Fourier Transform Analysis characteristics for *Vmabc* and *Vstat* voltage.

Page **6**